## DYNAMIC ENGINEERING

435 Park Dr., Ben Lomond, Calif. 95005 831-336-8891 Fax 831-336-3840 http://www.dyneng.com sales@dyneng.com Est. 1988

User Manual

## PCI-Serial-ECL

Programmable ECL IO with PCI DMA

Revision A2 Corresponding Hardware: Revision A/B 10-2004-0301, 10-2004-0302

#### PCI-Serial-ECL PCI based ECL IO w/ DMA

Dynamic Engineering 435 Park Drive Ben Lomond, CA 95005 831-336-8891 831-336-3840 FAX

©2004 by Dynamic Engineering.

Other trademarks and registered trademarks are owned by their

This document contains information of proprietary interest to Dynamic Engineering. It has been supplied in confidence and the recipient, by accepting this material, agrees that the subject matter will not be copied or reproduced, in whole or in part, nor its contents revealed in any manner or to any person except to meet the purpose for which it was delivered.

Dynamic Engineering has made every effort to ensure that this manual is accurate and complete. Still, the company reserves the right to make improvements or changes in the product described in this document at any time and without notice. Furthermore, Dynamic Engineering assumes no liability arising out of the application or use of the device described herein.

The electronic equipment described herein generates, uses, and can radiate radio frequency energy. Operation of this equipment in a residential area is likely to cause radio interference, in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

Dynamic Engineering's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Dynamic Engineering.

Connection of incompatible hardware is likely

respective manufactures.

Manual Revision A. Revised 6/18/04

# **Table of Contents**

| PRODUCT DESCRIPTION PART I                                                                                                                                                                           | 6                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| PRODUCT DESCRIPTION PART II                                                                                                                                                                          | 11                                                             |

| PROGRAMMING                                                                                                                                                                                          | 13                                                             |

| ADDRESS MAP                                                                                                                                                                                          | 14                                                             |

| Register Definitions PCISE BASE CNTL PCISE STATUS PCISE DMA FIFO PCISE EXT FIFO PCISE TTL PCISE ECL PCISE TX CNTR LD PCISE EXT FIFO CNT PCISE DMA AF CNT PCISE DMA AE CNT PCISE SWITCH PCISE INTSTAT | 15<br>15<br>20<br>21<br>22<br>23<br>23<br>24<br>24<br>25<br>25 |

| XILINX PIN OUT                                                                                                                                                                                       | 27                                                             |

| D100 STANDARD PIN ASSIGNMENT                                                                                                                                                                         | 33                                                             |

| APPLICATIONS GUIDE                                                                                                                                                                                   | 34                                                             |

| Interfacing                                                                                                                                                                                          | 34                                                             |

| Construction and Reliability                                                                                                                                                                         | 35                                                             |

| Thermal Considerations                                                                                                                                                                               | 35                                                             |

| WARRANTY AND REPAIR                                                                                                                                                                                  | 36                                                             |

| Out of Warranty Repairs | 37 |

|-------------------------|----|

| For Service Contact:    | 37 |

| <u>SPECIFICATIONS</u>   | 38 |

| ORDER INFORMATION       | 39 |

# List of Figures

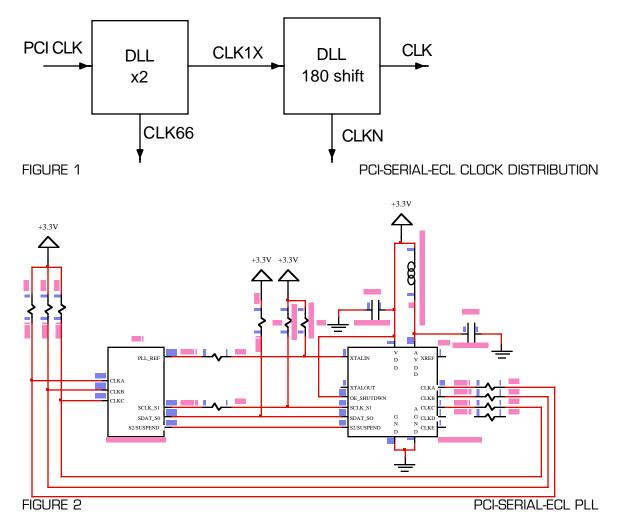

| FIGURE 1  | PCI-SERIAL-ECL CLOCK DISTRIBUTION            | 7  |

|-----------|----------------------------------------------|----|

| FIGURE 2  | PCI-SERIAL-ECL PLL                           | 7  |

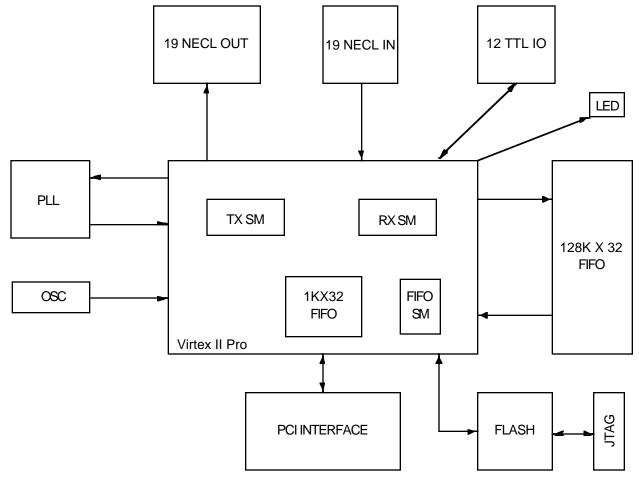

| FIGURE 3  | PCI-SERIAL-ECL BLOCK DIAGRAM                 | 9  |

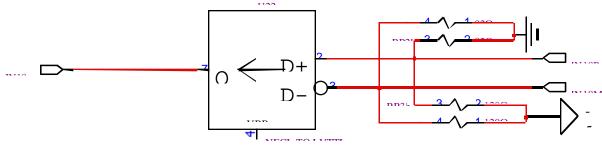

| FIGURE 4  | PCI-SERIAL-ECL TERMINATION                   | 10 |

| FIGURE 5  | PCI-SERIAL-ECL XILINX ADDRESS MAP            | 14 |

| FIGURE 6  | PCI-SERIAL-ECL XILINX BASE CONTROL REGISTER  | 15 |

| FIGURE 7  | PCI-SERIAL-ECL INTERRUPT ENABLE PORT         | 19 |

| FIGURE 8  | PCI-SERIAL-ECL STATUS PORT                   | 20 |

| FIGURE 9  | PCI-SERIAL-ECL DMA FIFO PORT                 | 21 |

| FIGURE 10 | PCI-SERIAL-ECL RX/TX FIFO PORT               | 22 |

| FIGURE 11 | PCI-SERIAL-ECL TTL CONTROL REGISTER          | 22 |

| FIGURE 12 | PCI-SERIAL-ECL ECL CONTROL REGISTER          | 23 |

| FIGURE 13 | PCI-SERIAL-ECL TX COUNTER LOAD PORT          | 23 |

| FIGURE 14 | PCI-SERIAL-ECL EXTERNAL FIFO DATA COUNT PORT | 24 |

| FIGURE 15 | PCI-SERIAL-ECL DMA FIFO PAF LEVEL REGISTER   | 24 |

| FIGURE 16 | PCI-SERIAL-ECL DMA FIFO PAE LEVEL REGISTER   | 25 |

| FIGURE 17 | PCI-SERIAL-ECL USER SWITCH PORT              | 25 |

| FIGURE 18 | PCI-SERIAL-ECL INTERRUPT STATUS PORT         | 26 |

| FIGURE 19 | PCI-SERIAL-ECL D100 PINOUT                   | 33 |

## Product Description Part I

PCI-Serial-ECL is part of the PCI Compatible family of modular I/O components. The PCI-Serial-ECL provides a Virtex II Pro FPGA, along with 38 ECL [NECL] and 12 TTL I/O lines, a programmable PLL and FIFO support with full DMA capabilities in a half-length single slot card.

The PCI bus implementation is 32 bits at 33 MHz, universal voltage. The hardware supports direct access software controlled read/write access to all locations plus DMA support to the high bandwidth ports. The hardware is optimized for back-to-back DMA accesses to support the multiple ports available on the PCI-Serial-ECL.

The PCI-Serial-ECL utilizes a PLX 9054 device for the PCI interface, and a Xilinx FPGA to manage the 9054 and provide the transmit and receive state-machine control. The 9054 supports scatter-gather DMA and the FPGA supports burst transfers to allow high speed DMA data transfers.

The external FIFO is a 128K x 32 device that can operate at 66 MHz. The FPGA features Block RAM that can be configured to provide additional FIFO or other memory to support the IO.

The transmit data path in a typical configuration uses DMA to move data from system memory to the external holding FIFO. The transmit state-machine would then read the data from the holding FIFO, reformat as required and transmit out of the ECL or TTL ports. Similarly if configured for receive the data is reformatted, any error checking performed and then loaded into the external FIFO. DMA will move the data from the FIFO to the system memory.

The Cypress 22393 PLL is handy for creating user specific frequencies with which to operate the state-machines and IO. The driver supports programming the PLL over a serial I2C bus. Three clocks are received from the PLL onto FPGA long-lines. The clock routing uses matched lengths to provide in-phase references should they be necessary in your design. The FPGA DLLs provide further clock functionality. The base clock tree uses the PCI clock and a pair of DLLs for low-skew on-chip distribution to generate an inverted clock and a 66 MHz in phase copy. The 66 MHz is routed to the PLL for its clock reference. A user Oscillator position is also provided to allow for custom frequencies to be generated when

the PLL programming is not exact enough for your application.

Cypress has a utility available for calculating the frequency control words for the PLL. <a href="http://www.dyneng.com/CyberClocks.zip">http://www.dyneng.com/CyberClocks.zip</a> is the URL for the Cypress software used to calculate the PLL programming words. The PLL responds to one of two addresses [only one works]. As part of our ATP our software determines the address of the PLL and prints it out. A label is attached to the shipping bag with the PLL addresses for the user's convenience. The software is part of the engineering kit and can be ported to your application

An 8-bit "dip switch" is provided on the PCI-Serial-ECL. The switch configuration is readable via a register. The switch is for user-defined purposes. We envision the

switch being used for software configuration control, PCI board identification or test purposes.

LEDs are provided on the board. One LED is attached to the the Xilinx via a register controlled pin. The LED initially flashes based in on the PCl clock divided down to a human viewable rate. Once software has initialized the card and taken control of the LED through the control bit it can be used for any purpose, e.g. to indicate bus traffic etc. In its initial mode the flashing LED can be interpreted to mean that the FPGA has successfully loaded. With new implementations of VHDL it is handy to have "proof" that the Xilinx has been loaded, especially when the design is not behaving as expected.

An additional LED is provided to indicate that the 3.3V regulator is operating properly. Local regulation is provided for 3.3, 2.5,1.5, and -5V volts. The 3.3V supply has a shunt to select between the backplane 3.3 and the local regulator. The local regulator is a switching power supply which drops the 5V rail to 3.3V. The supply can source up to 1OA. The -5V is needed for the ECL and is rated at 3A. The 1.5 and 2.5 are used by the Xilinx and have a lower capacity.

FIGURE 3 PCI-SERIAL-ECL BLOCK DIAGRAM

The PCI-Serial-ECL has both ECL and TTL IO interfaced by a D100 connector.

The TTL IO [11-0] is supported with open drain drivers with pull-ups and high-speed receivers [LVC244]. We have operated the board at 100 MHz through the TTL signals over short cables. The open drain drivers [LVTH125] have 64+mA of sink capability.

There are 38 un-committed ECL IO. 19 devices are inputs and 19 are outputs. The inputs are terminated with  $50\Omega$  to -2V using a parallel equivalent circuit. [82/120] The ECL lines are routed as differential pairs with matched lengths and constant space. The lengths are matched from the connector edge to the Xilinx ball to allow for high-speed low skew operation.

FIGURE 4 PCI-SERIAL-ECL TERMINATION

The Xilinx FPGA is re-configurable by loading a new programming file into the FLASH storage device. The file can be generated with the standard Xilinx design software. The standard Xilinx Parallel JTAG cable is connected to the on-board header to program the FLASH using the Xilinx ImPACT software. A reference file with our test configuration is also provided. The reference design has a pin configuration file, which can be reused for your specific implementation. The reference design is written in VHDL. The engineering kit also includes a cable and the HDEterm100. The HDEterm100 serves as a breakout from the cable to screw terminal block. The HDEterm100 has matched length, differential routing and several termination options that can be installed. For more information on the HDEterm100 please visit the web page <a href="http://www.dyneng.com/HDEterm100.html">http://www.dyneng.com/HDEterm100.html</a>

## Product Description Part II

A wide range of interfaces and protocols can be implemented with the PCI-Serial-ECL. UART, Manchester encoding, serial or parallel, ECL/NECL or TTL. The interfaces can be created using the hardware and development tools provided with the PCI-Serial-ECL along with the Xilinx software.

Once your requirements are known the design can be implemented with VHDL, Verilog, or schematics and compiled with the Xilinx design software. The output file can then be "uploaded" to the Xilinx FPGA [FLASH] on the PCI-Serial-ECL. Because the FPGA can be re-loaded, your design can be implemented in phases. You can experiment and test out concepts and partial implementations during the design phase or perhaps simulate other hardware that needs to be implemented.

As an example consider a serial interface with 3 signals. The PCI-Serial-ECL has 38 ECL differential IO. There are enough IO for 1 full duplex channel with a clock reference, data and enable. The equivalent of a 16-bit parallel port would be left plus the 12 TTL IO. The serial channel would be supported with the 128Kx32 external FIFO plus any internal FIFOs that were instantiated out of block RAM. If the memory requirement per channel is small then additional channels can be supported on the one card. The FPGA is a Virtex II Pro model 4 and has plenty of additional room for more complex or additional data formatting requirements.

For systems with an external reference clock, the upper ECL input bit is received by the FPGA on a long line pin. IN18P/N can be routed through a DLL to create a low skew clock distribution based on an external reference.

The data flow for transmission would be Host memory transferred into the DMA FIFO (internal to the Xilinx) via DMA transfers. From the DMA FIFO to the TX channel FIFO (external FIFO used for transmission). The user state machine would read the data from the FIFO on the output side and apply the user protocol before serializing and transmitting. On the receive side the data would flow into the FPGA, be processed to convert to a format suitable for storing, and be written into the RX FIFO (external FIFO when configured for receive). The data would be read from the RX FIFO by the Xilinx state-machine and be transferred into the DMA FIFO before being transferred to the host memory.

The full bandwidth of the PCI bus is utilized during DMA transfers. There is some

overhead on the PCI bus side, which will limit the actual sustainable transfer rate somewhat compared to the theoretical limit. Looking at the other side of the equation: if we assume serial data with 1 channel operating at 170 MHz, this creates a total of 5.313 Mwords per second on the PCI bus – approximately 16% loading of the theoretical maximum.

Using the same example and looking at the external FIFO one can see that the OS can "go away" for 170 Mbits/sec / 32 / 128 K => 24.7 mS without over-running or under-running the FIFO. With Windows® and other high level OS based system the OS can loose track of the data movement due to other requirements - dealing with the keyboard or HDD for example. Having adequate storage can make a big difference in system performance.

#### Current Feature List

- User Definable Xilinx Virtex II Pro series FPGA

- DMA capable 32/33 PCI bus interface

- PLL

- 128K x 32 Data buffer

- 19 ECL Outputs

- 19 ECL Inputs

- 12 TTL IO

- 8 position "DIP Switch"

- User LED

- Power LED

- On going development with a "PROM" program

As Dynamic Engineering adds features to the hardware we will update the PCI-Serial-ECL page on the Dynamic Engineering website. If you want some of the new features, and have already purchased hardware, we will support you with a PROM update. We will reprogram the FLASH on your board for you or if you have the engineering kit and your own download cable, send you the new bit file. If you are interested please contact <a href="mailto:sales@dyneng.com">sales@dyneng.com</a> for arrangements.

The basic PCI identifying information will not change with the updates. The revision field will change to allow configuration control. Current revision is 0x00.

## **Programming**

The PCI-SERIAL-ECL is tested in a Windows® 2000 environment. We use our driver to support our test software. Please consider purchasing the engineering kit for the PCI-SERIAL-ECL; the kit has options and can include our test suite, driver and hardware support.

Before communication with the Xilinx device can happen the PLX device requires some initialization. The local bus address space must be enabled and if interrupts are to be used the PLX must be enabled for these too.

Writing to the PLX local configuration address offset Ox4 (LASOBA) with OxO1 will enable the local bus for memory space access, and re-map the local address to offset O.

Writing to the Bus Region Descriptors 0x18 (LBRDO) with 0x40430343 will put the local bus into a well behaved state to inter-operate with the Xilinx. Specifically we are disabling the pre-fetch capability for the memory and ROM spaces. With the FIFO interfaces pre-fetching, possible loss of data can occur. More detail is available in the PLX 9054 HW design manual.

Writing 0x01200000 to 0x08 (MARBR) will set the Mode/DMA Arbitration to the correct state for operation.

To use interrupts from the Xilinx, Ox68 (INTCSR) will need to be programmed. OxOFO00900 will enable the local bus interrupt and PCI interrupt capability. To disable the local side interrupt clear bit 11.

Operation with DMA requires additional register programming within the PLX and Xilinx devices. The Dynamic Engineering Driver takes care of all of the initialization if it is used. Windows 2000 and XP are currently supported.

The internal registers for the Xilinx are defined in the following pages.

## Address Map

| PCISE_INTEN OX PCISE_STATUS OX PCISE_SLAVE OX PCISE_FIFO OX PCISE_TIL_DATA_OUT OX PCISE_TIL_DATA_IN OX PCISE_ECL_OUT OX PCISE_ECL_IN OX PCISE_LOAD_TX_CNTR OX PCISE_EXT_FIFO_CNT OX PCISE_DMA_FIFO_AF_LVL OX PCISE_DMA_FIFO_AE_LVL OX PCISE_SWITCH OX PCISE_INTSTAT OX | 0000000 //0 base control register 00000004 //1 interrupt enable register 00000008 //2 status - read 0000000C //3 DMA FIFO read - write single word 00000010 //4 External FIFO read - write single word 00000014 //5 TTL Reg read/write 00000018 //6 TTL IO read only 0000001C //7 ECL output port for parallel data 00000020 //8 ECL input port for parallel data 00000024 //9 start value for transmit counter 00000028 //10 External FIFO data count - read 00000026 //11 DMA FIFO almost full level read/write 00000030 //12 DMA FIFO almost empty level read/write 00000034 //13 User Switch read back port 00000036 //15 int stat clr - write, int stat - read |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

FIGURE 5

PCI-SERIAL-ECL XILINX ADDRESS MAP

The address map provided is for the local decoding performed within PCI-Serial-ECL Xilinx. The addresses are all offsets from a base address. The base address and interrupt level are provided by the host in which the PCI-Serial-ECL is installed.

The host system will search the PCI bus to find the assets installed during poweron initialization and allocate memory and interrupt resources. The Vendorld = 0x10b5 and the CardId = 0x9054 for the PCI-Serial-ECL. PCIView or other third party utilities can be useful to view your system configuration.

Once the initialization process has occurred and the system has assigned an address range to the PCI-Serial-ECL card, the software will need to determine what the address space is. We refer to this address as baseO in our software.

The next step is to initialize the PCI-Serial-ECL. The local Xilinx registers need to be configured.

## Register Definitions

#### PCISE\_BASE\_CNTL

[\$0000 Main Control Register Port read/write]

|                                                                          | BASE REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA BIT                                                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 21 31 30 29 28 27-25 24 22 21 20 19-17 16 15-14 12 11-10 9 8 7 6 5 4 3-1 | Start_RX '1' enables RX state machine Mux Sel '1' Enable TX counter data instead of FIFO data Start_TX_B '1' enables transmit state machine to transmit Start_TX_A '1' enables state machine to load external FIFO from internal FIFO spare Ext FIFO LD '1' enables programming almost full/empty FIFO flag levels PLL En '1' = software enable to program PLL PLL Data register bit PLL S2 PLL SCLK output = PLL Command Clock spare EXT FIFO RST '1' resets external FIFO O = normal operation spare m_int_en - interrupt driver enable, master interrupt enable force_int - cause an interrupt by enabling this bit spare led_on - '1' lights Xilinx LED, '0' turns LED off led_en - '1' enabled to register control, O = blinking en_wr_dma - enable the write FIFO state machine for DMA operation en_rd_dma - enable the read FIFO state machine for DMA operation en_wr_std - enable the read FIFO state machine for single word access en_rd_std - enable the read FIFO state machine for single word access spare |

| 0                                                                        | dma_rst '1' resets DMA FIFO, '0' for normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### FIGURE 6

#### PCI-SERIAL-ECL XILINX BASE CONTROL REGISTER

M\_INT\_EN is the master interrupt enable for all interrupts on the PCI-Serial-ECL which are controlled by the Xilinx. Please note that the PLX interrupt enable must also be enabled for a PCI interrupt to be generated. Default is disabled. When '1' the master enable is "enabled".

FORCE\_INT when '1' and the master enabled causes an interrupt to be generated. This bit is useful for software debugging.

LED\_ON when '1' enables the Xilinx controlled LED. This bit works in conjunction with the LED\_EN. When LED\_EN = '0' the internal timer causes the LED to flash. When LED\_EN = '1' the register bit LED\_ON controls the LED. When the board is powered on and the LED is flashing the Xilinx has successfully loaded. When the software takes control the flashing will stop and a new user defined meaning attached to the LED. The user LED is located next to the 3.3V LED on the upper portion of the board.

EN\_WR\_DMA when '1' enables the state-machine to support DMA transferred write operations into the DMA FIFO.

EN\_RD\_DMA when '1' enables the state-machine to support DMA transferred read operations into the DMA FIFO.

EN\_WR\_STD when '1' enables the state-machine to support single word write operations into the DMA FIFO.

EN\_RD\_STD when '1' enables the state-machine to support single word read operations into the DMA FIFO.

Ext FIFO LD when '1' selects the programming mode for the Programmable Almost Empty and Programmable Almost Full flag on the External FIFO. 'O' is normal operation.

To program the FIFO flag first set the Ext FIFO LD bit, then set and clear the EXT FIFO RST bit. The next sequence of data written to the FIFOs will program the flags. When the sequence is completed take Ext FIFO LD low. Please note that you do not reset the part again. If reset occurs after programming the flags, the flags will revert to the default values.

The 128Kx32 part used on the PCI-Serial-ECL has a17-bit range for the PAE and PAF flags. The PAE flag is written first. The default is 127. The bit positions are LSB aligned [D16-O]. The PAF flag does not have to be written in order to program the PAE. If the PAF value is not written then it will require a reset to rewrite the PAE values. If the PAF values are written then the pointer is returned to the PAE location. The PAE value can be re-written by setting the Ext FIFO LD bit and repeating the load sequence.

EXT FIFO RST when '1' resets the external FIFO. Set to '0' for normal operation.

To guarantee proper operation, the FIFO should be reset after power up. Set the reset control bit and then clear the control bit. The reset should be applied after the clocks are stable. The reset signal meets set-up and hold times. The Xilinx takes care of these requirements automatically. The on time is short enough that software can toggle the bit as rapidly as desired.

DMA\_RST when set to '1' will reset the DMA FIFO. Set to '0' for normal operation.

The PCI-Serial-ECL has 1 PLL device that is programmed to produce the desired frequency with an I2C bus.

The data line has a pull-up on the board. When the I2C data bit is set to 'O' in the register the external line is driven low. When the I2C data is set to '1' in the register the external line is pulled-up by the resistor. For a read operation the data should be set to '1' to allow the PLL to drive the line.

The upper selection bit can be set in the register and directly driven to the PLL.

The clock line for the PLL to be programmed is toggled along with the data to create a bit stream with a "software clock". Set the bit to the next state and toggle the clock line repeat.

To read over the I2C bus a command is first written and then the bus read for the response. The I2C clock and I2C data register bits contain the state of the bus when read. The software will poll the clock line and when the high to low transition is made read the data bit then repeat until the message is captured. Please note that the data bit in this register corresponds to the read/write register. The read-back data bit is located in the status register.

The engineering kit contains the logic and software required to program the PLL and to read the programmed frequency back. The software to determine the frequency command words is available from Cypress Semiconductor. The part number is CY22393FC. The command word generation program is downloadable from the Dynamic Engineering site.

In the base design the transmit clock is defined by the PLL output clock A. The reference to the PLL is the PCI clock doubled (66 MHz).

Start\_TX\_A and Start\_TX\_B are used to control the initialization of and transfer of data with the transmit state-machine. Start\_TX\_A when set causes the state-machine to start moving data from the internal "DMA FIFO" to the external data storage register. When there is sufficient data in the external FIFO Start\_TX\_B can be set to cause the TX state-machine to begin to send data to the Output. Depending on the system configuration different amounts of data should be stored into the external FIFO before starting the data transfer.

MUX\_SEL when '1' causes the transmitter to use locally generated data instead of the stored External FIFO data for the transmission. The 32-bit counter is preloadable with an arbitrary offset. The counter is used to allow the receive section to be tested with the transmit section on the same card (there is only one storage FIFO).

Start\_RX when set causes the RX state-machine to look for data. When data is recognized it is captured and then stored into the external FIFO using the preprogrammed algorithm.

#### PCISE INTEN

[\$0004 Interrupt Enable Port read/write]

|                                 | INTERRUPT ENABLE REGISTER                                                          |  |

|---------------------------------|------------------------------------------------------------------------------------|--|

| DATA BIT                        | DESCRIPTION                                                                        |  |

| 6<br>5<br>4<br>3<br>2<br>1<br>0 | inten_rx_or inten_tx_dn inten_ecl_in inten_dma_ae inten_dma_af inten_pae inten_paf |  |

#### FIGURE 7

#### PCI-SERIAL-ECL INTERRUPT ENABLE PORT

Inten\_paf when '1' enables the Programmable Almost Full interrupt for the external FIFO.

Inten\_pae when '1' enables the Programmable Almost Empty interrupt for the external FIFO.

Inten\_dma\_af when '1' enables the Programmable Almost Full interrupt for the internal (DMA) FIFO.

Inten\_dma\_ae when '1' enables the Programmable Almost Empty interrupt for the internal (DMA) FIFO.

Inten\_ecl\_in when '1' enables the ECL input interrupt, which generates an interrupt when a low to high transition occurs on ECL\_IN(O).

Inten\_tx\_dn when '1' enables the interrupt for the transmitter done condition. This occurs when the external FIFO does not have data when the transmitter is ready to read the next data word. This causes the START\_TX\_B bit to be cleared and the tx state-machine to halt.

Inten\_rx\_or when '1' enables the interrupt for the receiver over-run condition. Over-run occurs when the receiver is ready to load a data word and the external FIFO is full.

#### PCISE\_STATUS

[\$0008 Status Port read only]

|                                                                                            | STATUS REGISTER                                                                                                                                                      |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA BIT                                                                                   | DESCRIPTION                                                                                                                                                          |

| 31-25<br>24<br>23<br>22<br>20,21<br>19<br>18<br>17<br>16<br>15<br>14<br>13<br>12<br>11 - 0 | undefined and special purpose bits dma_valid ext_valid pll_sdat - read-back bit spare fifo_ff fifo_paf fifo_pae fifo_mt dma_ff dma_paf dma_pae dma_mt dma_fifo_count |

FIGURE 8

PCI-SERIAL-ECL STATUS PORT

DMA\_FIFO\_COUNT indicates the number of data words in the DMA FIFO. There is always one more word available than this count indicates, since one read occurs automatically as soon as data is written to the FIFO. This data word is held in the output register until requested.

DMA\_MT when '1' indicates that the DMA FIFO is empty.

DMA\_PAE when '1' indicates that the DMA FIFO is almost empty as determined by the almost empty register value.

DMA\_PAF when '1' indicates that the DMA FIFO is almost full as determined by the almost full register value.

20

DMA\_FF when '1' indicates that the DMA FIFO is full.

FIFO\_MT when '1' indicates that the external FIFO is empty.

FIFO PAE = External FIFO Programmable Almost Empty flag. When '1' the FIFO is almost empty.

FIFO PAF = External FIFO Programmable Almost Full flag. When '1' the external FIFO is almost full.

The programmable FIFO levels can be changed from the default values using the procedure described in the Base control register description.

FIFO\_FF when '1' indicates that the external FIFO is full.

PLL\_SDAT is the read-back bit to get the state of the data line connected to the PLL with the I2C bus. When reading data from the PLL this bit must be used.

EXT\_VALID when '1' indicates that there is valid data available from the external FIFO. This bit may be set even when the FIFO is empty since there are two data words held in the FIFO output registers.

DMA\_VALID when '1' indicates that there is valid data available from the DMA FIFO. This bit may be set even when the FIFO is empty since there is one data word held in the FIFO output register.

The bits in this register are unlatched and unmasked. The Interrupt Status latch contains latched data bits corresponding to each interrupt cause.

#### PCISE DMA FIFO

[\$000C, 0x0040 DMA FIF0 Port]

|          | DMA FIFO PORT     |  |

|----------|-------------------|--|

| DATA BIT | DESCRIPTION       |  |

| 310      | DMA FIFO data 310 |  |

|          |                   |  |

FIGURE 9

PCI-SERIAL-ECL DMA FIFO PORT

The DMA FIFO can be written to or read from via the PCI bus. The DMA FIFO can be accessed with "standard" [OxOOC] target accesses or via DMA[OxOO4O]. The base control register must be properly programmed before accessing this port.

#### PCISE\_EXT\_FIFO

#### [OxOO10 External FIFO Port]

|          | EXTERNAL FIFO PORT |  |

|----------|--------------------|--|

| DATA BIT | DESCRIPTION        |  |

| 310      | FIFO Data 310      |  |

FIGURE 10

PCI-SERIAL-ECL RX/TX FIFO PORT

A write to the port causes a write to the external FIFO. A read from the port causes a read from the external FIFO. The data width of the FIFO is 32 bits. The direct read and write port is used for testing and special conditions.

The port can be used for loop-back testing with DMA'd or direct writes to the External FIFO followed by reads from the External FIFO port.

#### PCISE\_TTL

[Ox14, 18 TTL Control Ports read/write] PCISE\_TTL\_DATA\_OUT, PCISE\_TTL\_DATA\_IN

|          | TTL IO REGISTERS |  |

|----------|------------------|--|

| DATA BIT | DESCRIPTION      |  |

| 11-0     | TTL 11 - O       |  |

FIGURE 11

PCI-SERIAL-ECL TTL CONTROL REGISTER

The TTL IO are designed with a '125 style gate and read-back buffer. The '125 provides an "open drain" tri-state gate. The PCI-Serial-ECL has a pull-up on each line. When the gate is enabled the corresponding line is pulled low. When the gate is disabled the line is pulled-high with the pull-up.

In order for the TTL port to be used for input, the output must be set to "FFF" to cause the IO to be in the tri-stated condition. The software can write a '1' or 'O' to any bit and cause the '1' or 'O' on the IO line. If an external line is driving the IO bit then the line may remain at 'O' when set to the un-driven state.

The read port [PCISE\_TTL\_DATA\_IN] returns the state of the IO lines – not necessarily the same as the write port.

#### PCISE\_ECL

[Ox1C, 20 ECL Control Ports read/write] PCISE\_ECL\_OUT, PCISE\_ECL\_IN

|          | ECL IO REGISTERS |  |

|----------|------------------|--|

| DATA BIT | DESCRIPTION      |  |

| 15-0     | ECL 15 - 0       |  |

#### FIGURE 12

#### PCI-SERIAL-ECL ECL CONTROL REGISTER

The ECL IO lines not used for the serial port are organized as a parallel port. In the base design there are 16 input and 16 output lines. The outputs are driven from the register definition [PCISE\_ECL\_OUT]. The inputs are read from the receivers [PCISE\_ECL\_IN].

#### PCISE\_TX\_CNTR\_LD

[Ox24 Control Port read/write]

|          | TX COUNTER LOAD REGISTER |

|----------|--------------------------|

| DATA BIT | DESCRIPTION              |

| 31-0     | TX Counter Initial Value |

|          |                          |

#### FIGURE 13

#### PCI-SERIAL-ECL TX COUNTER LOAD PORT

The serial transmit data can be derived from an internal 32-bit counter. This port allows that counter to be initialized to an arbitrary value. Thereafter each data value will be incremented by one from the previous value.

#### PCISE\_EXT\_FIFO\_CNT

[Ox28 Status Port read only]

| EXTERNAL FIFO WORD COUNT |             |  |

|--------------------------|-------------|--|

| DATA BIT                 | DESCRIPTION |  |

| 15-0                     | ECL 15 - 0  |  |

FIGURE 14

PCI-SERIAL-ECL EXTERNAL FIFO DATA COUNT PORT

Reading this port returns the number of data words in the External FIFO. There are always two more words available than this count indicates, since two reads occurs automatically as soon as data is written to the FIFO. These data words are held in the output registers until requested.

#### PCISE\_DMA\_AF\_CNT

[Ox2C Control Port read/write]

| DMA FIFO PAF REGISTER |             |  |

|-----------------------|-------------|--|

| DATA BIT              | DESCRIPTION |  |

| 15-O PAF Level 15 - O |             |  |

FIGURE 15

PCI-SERIAL-ECL DMA FIFO PAF LEVEL REGISTER

The value in this register is compared to the DMA FIFO count. If the count is greater than or equal to the value in this register, the DMA almost full status bit is set and the DMA almost full interrupt status bit is latched and may cause an interrupt if the proper enables are set.

#### PCISE\_DMA\_AE\_CNT

[Ox30 Control Port read/write]

| DMA FIFO PAE REGISTER |  |  |

|-----------------------|--|--|

| DATA BIT DESCRIPTION  |  |  |

| 15-O PAE Level 15 - O |  |  |

FIGURE 16

PCI-SERIAL-ECL DMA FIFO PAE LEVEL REGISTER

The value in this register is compared to the DMA FIFO count. If the count is less than or equal to the value in this register, the DMA almost empty status bit is set and the DMA almost empty interrupt status bit is latched and may cause an interrupt if the proper enables are set.

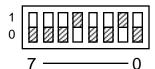

#### PCISE SWITCH

[\$0034 User Switch Port read only]

|          | DIPSWITCH PORT |  |

|----------|----------------|--|

| DATA BIT | DESCRIPTION    |  |

| 70       | Sw70           |  |

|          |                |  |

FIGURE 17

PCI-SERIAL-ECL USER SWITCH PORT

The user switch is read through this port. The bits are read as the lowest byte. Access the port as a long word and mask off the undefined bits. Read only. The dipswitch positions are defined in the silkscreen. For example the switch figure below indicates a 0x12.

#### PCISE INTSTAT

[OxOO3C Interrupt Status Port]

|                                      | INTERRUPT STATUS PORT                                                         |  |

|--------------------------------------|-------------------------------------------------------------------------------|--|

| DATA BIT                             | DESCRIPTION                                                                   |  |

| 7<br>6<br>5<br>4<br>3<br>2<br>1<br>0 | gnd<br>RX_OR_ERR<br>TX_DN<br>ECL_IN<br>DMA_AE<br>DMA_AF<br>EXT_PAE<br>EXT_PAF |  |

FIGURE 18

PCI-SERIAL-ECL INTERRUPT STATUS PORT

The Programmable Almost Empty and Programmable Almost Full flags are captured on the transition to active and held until explicitly cleared. The associated interrupt would be used to keep the data flowing to the transmit port and to prevent overflow on the receive port.

ECL\_IN is latched as a '1' when a low to high transition occurs on the ECL\_IN(O) input data bit.

TX\_DN is latched high when the transmit state-machine runs out of FIFO data to send.

RX\_OR\_ERR is the latched version of the over-run error condition. This occurs when the receive state machine tries to load data into a full FIFO.

To clear the status, write to the port with the associated bit set.

## Xilinx Pin Out

The FPGA pin definitions are contained in the engineering kit and repeated here as a reference. The hardwired pins for power, ground, programming etc. are not shown.

| NET       "clkFlFOin"       LOC=         NET       "FIN_REN"       LOC=         NET       "FOUT_WEN"       LOC=         NET       "FOUT_RSTN"       LOC=         NET       "FOUT_W_LD"       LOC=         NET       "FOUT_PAEN"       LOC=         NET       "FIN_PAFN"       LOC=         NET       "FIFO_MTN"       LOC=                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ="C22";<br>="F22";<br>="E22";<br>="D22";<br>="F18";<br>="F19";<br>="G18";<br>="F21";<br>="G19";                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NET         "FOUT_WEN"         LOC=           NET         "FOUT_RSTN"         LOC=           NET         "FOUT_W_LD"         LOC=           NET         "FOUT_PAEN"         LOC=           NET         "FIN_PAFN"         LOC=           NET         "FIFO_MTN"         LOC=                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ="D22";<br>="F18";<br>="F19";<br>="G18";<br>="F21";<br>="G19";                                                                                                                                                                                                                                                       |

| INC. III O_IIIN LOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                      |

| NET         "FDAT_IN<1>"         LOC           NET         "FDAT_IN<2>"         LOC           NET         "FDAT_IN<3>"         LOC           NET         "FDAT_IN<4>"         LOC           NET         "FDAT_IN<5>"         LOC           NET         "FDAT_IN<6>"         LOC           NET         "FDAT_IN<6>"         LOC           NET         "FDAT_IN<8>"         LOC           NET         "FDAT_IN<8>"         LOC           NET         "FDAT_IN<10>"         LOC           NET         "FDAT_IN<11>"         LOC           NET         "FDAT_IN<12>"         LOC           NET         "FDAT_IN<13>"         LOC           NET         "FDAT_IN<16>"         LOC           NET         "FDAT_IN<16>"         LOC           NET         "FDAT_IN<16>"         LOC           NET         "FDAT_IN<210>"         LOC           NET         "FDAT_IN<20>"         LOC           NET         "FDAT_IN<20>"         LOC           NET         "FDAT_IN<220>"         LOC           NET         "FDAT_IN<223>"         LOC           NET         "FDAT_IN<225>"         LOC           NET< | = "U21";<br>= "U20";<br>= "T22";<br>= "T20";<br>= "T19";<br>= "T19";<br>= "R22";<br>= "R20";<br>= "R20";<br>= "R19";<br>= "R19";<br>= "P21";<br>= "N17";<br>= "N17";<br>= "N17";<br>= "M20";<br>= "M18";<br>= "L21";<br>= "L19";<br>= "K21";<br>= "K19";<br>= "K19";<br>= "K19";<br>= "J21";<br>= "J21";<br>= "J19"; |

```

LOC = "J17";

NET

"FDAT_IN<28>"

NET

"FDAT IN<29>"

LOC = "H22":

LOC = "H2O";

NET

"FDAT IN<30>"

NET

"FDAT_IN<31>"

LOC = "H18";

NET

"FDAT_OUT<0>"

LOC = "AA22";

NET

"FDAT OUT<1>"

LOC = "Y21";

NET

"FDAT OUT<2>"

LOC = "Y22":

"FDAT OUT<3>"

LOC = "W21";

NET

"FDAT_OUT<4>"

NET

LOC = "W22";

LOC = "V20";

NET

"FDAT OUT<5>"

LOC = "V19";

NET

"FDAT OUT<6>"

"FDAT_OUT<7>"

LOC = "V21";

NET

NET

"FDAT OUT<8>"

LOC = "V22";

NET

"FDAT OUT<9>"

LOC = "U22":

NET

"FDAT OUT<10>"

LOC = "P22";

NET

"FDAT_OUT<11>"

LOC = "P2O";

"FDAT OUT<12>"

LOC = "P18";

NET

NET

"FDAT OUT<13>"

LOC = "N22";

"FDAT OUT<14>"

LOC = "N2O";

NET

"FDAT_OUT<15>"

LOC = "N18";

NET

NET

"FDAT OUT<16>"

LOC = "M21";

NET

"FDAT_OUT<17>"

LOC = "M19";

"FDAT OUT<18>"

NET

LOC = "M17";

"FDAT OUT<19>"

LOC = "L2O";

NET

NET

"FDAT OUT<20>"

LOC = "L18";

NET

"FDAT_OUT<21>"

LOC = "K22";

NET

"FDAT_OUT<22>"

LOC = "K20";

"FDAT OUT<23>"

LOC = "K18";

NET

LOC = "J22";

NET

"FDAT OUT<24>"

"FDAT OUT<25>"

LOC = "J20";

NET

NET

"FDAT_OUT<26>"

LOC = "J18";

NET

"FDAT OUT<27>"

LOC = "H21";

NET

"FDAT OUT<28>"

LOC = "H19";

NET

"FDAT_OUT<29>"

LOC = "G22";

"FDAT OUT<30>"

LOC = "G21";

NET

NET

"FDAT OUT<31>"

LOC = "G2O";

### PLX Interface - In pin order on PLX device to help with Xilinx pin definitions

NET

"CLKIN"

LOC = "C11"; #PLX CLOCK

NET

"ADDRESS<5>"

LOC = "AB21";

LOC = "W18";

NET

"ADDRESS<4>"

LOC = "U19";

NET

"ADDRESS<3>"

NET

"ADDRESS<2>"

LOC = "U18";

LOC = "V16":

NET

"ADDRESS<1>"

NET

"ADDRESS<0>"

LOC = "W16";

NET

"W_R"

LOC = "Y16";

```

```

NET

"DATA IOP<31>"

LOC = "R1";

LOC = "V15";

NET

"DATA IOP<30>"

NET

"DATA IOP<29>"

LOC = "W15";

"DATA_IOP<28>"

NET

LOC = "Y15";

NET

"DATA_IOP<27>"

LOC = "U14";

NET

"DATA IOP<26>"

LOC = "V14";

NET

"DATA IOP<25>"

LOC = "W14";

LOC = "W13";

NET

"DATA IOP<24>"

NET

"DATA_IOP<23>"

LOC = "U13";

NET

"DATA IOP<22>"

LOC = "V13";

NET

"DATA IOP<21>"

LOC = "AA12";

NET

"DATA IOP<20>"

LOC = "U12";

"DATA IOP<19>"

LOC = "V12";

NET

NET

"DATA IOP<18>"

LOC = "W12";

NET

"DATA IOP<17>"

LOC = "Y12";

NET

"DATA_IOP<16>"

LOC = "Y11";

LOC = "W11";

NET

"DATA IOP<15>"

NET

"DATA IOP<14>"

LOC = "V11";

"DATA IOP<13>"

LOC = "U11";

NET

LOC = "AA11";

NET

"DATA_IOP<12>"

NET

"DATA IOP<11>"

LOC = "Y10";

NET

"DATA_IOP<10>"

LOC = "V10";

NET

"DATA IOP<9>"

LOC = "U10";

LOC = "W10";

NET

"DATA IOP<8>"

NET

"DATA IOP<7>"

LOC = "W9";

NET

"DATA IOP<6>"

LOC = "V9";

NET

"DATA_IOP<5>"

LOC = "U9";

LOC = "Y8";

NET

"DATA IOP<4>"

LOC = "W8";

NET

"DATA IOP<3>"

LOC = "Y7";

NET

"DATA IOP<2>"

NET

"DATA_IOP<1>"

LOC = "W7";

NET

"DATA IOP<0>"

LOC = "V7";

LOC = "V6";

NET

"READYN"

LOC = "W6";

NET

"ADSN"

NET

"BLASTN"

LOC = "W5";

LOC = "AB2";

NET

"RSTN"

NET

"LINTN"

LOC = "AA1";

LOC = "C10";

NET

"switch in<0>"

NET

"switch in<1>"

LOC = "C8";

LOC = "C7";

NET

"switch_in<2>"

NET

"switch in<3>"

LOC = "D7";

NET

LOC = "D6";

"switch_in<4>"

NET

"switch in<5>"

LOC = "D5";

NET

"switch in<6>"

LOC = "C2";

NET

"switch in<7>"

LOC = "C1";

```

| NET                                                                | "LED"                                                                                                                                                          | LOC ="C21";                                                                                                                                                                      |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NET<br>NET<br>NET<br>NET<br>NET<br>NET<br>NET                      | "CLKA" "CLKB" "CLKC" "PLL_REF" "PLL_SCLK" "PLL_SDAT" "PLL_S2"                                                                                                  | LOC ="D11";<br>LOC ="D12";<br>LOC ="E11";<br>LOC ="B11";<br>LOC ="B12";<br>LOC ="C13";<br>LOC ="D13";                                                                            |

| NET<br>NET<br>NET<br>NET<br>NET<br>NET<br>NET<br>NET<br>NET<br>NET | "TTL_IN<0>" "TTL_IN<1>" "TTL_IN<2>" "TTL_IN<3>" "TTL_IN<4>" "TTL_IN<5>" "TTL_IN<6>" "TTL_IN<7>" "TTL_IN<8>" "TTL_IN<9>" "TTL_IN<10>" "TTL_IN<11>" "TTL_IN<10>" | LOC = "J1";<br>LOC = "J2";<br>LOC = "J3";<br>LOC = "J4";<br>LOC = "H1";<br>LOC = "H2";<br>LOC = "H4";<br>LOC = "H4";<br>LOC = "H5";<br>LOC = "G5";<br>LOC = "G5";                |

| NET                            | "TTL_OUT<0>" "TTL_OUT<1>" "TTL_OUT<2>" "TTL_OUT<3>" "TTL_OUT<4>" "TTL_OUT<5>" "TTL_OUT<6>" "TTL_OUT<7>" "TTL_OUT<8>" "TTL_OUT<9>" "TTL_OUT<10>" "TTL_OUT<11>"  | LOC = "G1";<br>LOC = "G2";<br>LOC = "F1";<br>LOC = "F2";<br>LOC = "F4";<br>LOC = "E1";<br>LOC = "E2";<br>LOC = "E3";<br>LOC = "E4";<br>LOC = "E4";<br>LOC = "D1";<br>LOC = "D2"; |

| NET                            | "ECL_IN<0>" "ECL_IN<1>" "ECL_IN<2>" "ECL_IN<3>" "ECL_IN<5>" "ECL_IN<6>" "ECL_IN<6>" "ECL_IN<7>" "ECL_IN<8>" "ECL_IN<9>" "ECL_IN<10>" "ECL_IN<11>"              | LOC = "Y1";<br>LOC = "Y2";<br>LOC = "W1";<br>LOC = "V2";<br>LOC = "V2";<br>LOC = "V3";<br>LOC = "V4";<br>LOC = "U4";<br>LOC = "U1";<br>LOC = "U2";<br>LOC = "U3";<br>LOC = "U4"; |

```

"ECL IN<12>"

LOC = "U5";

NET

LOC = "T1":

NET

"ECL IN<13>"

"ECL IN<14>"

LOC = "T2":

NET

NET

"ECL IN<15>"

LOC = "T3":

LOC = "T4";

NET

"ECL IN<16>"

LOC = "T5";

NET

"ECL IN<17>"

LOC = "C12";

NET

"ECL IN<18>"

"ECL OUT<0>"

NET

LOC = "N1":

NET

"ECL OUT<1>"

LOC = "N2"

NET

"ECL OUT<2>"

LOC = "N3";

LOC = "N4":

NET

"ECL OUT<3>"

"ECL OUT<4>"

LOC = "N5":

NET

NET

"ECL OUT<5>"

LOC = "M2"

NET

"ECL OUT<6>"

LOC = "M3":

NET

"ECL OUT<7>"

LOC = "M4";

LOC = "M5"

NET

"ECL OUT<8>"

NET

"ECL OUT<9>"

LOC = "L2";

NET

"ECL OUT<10>"

LOC = "L3":

LOC = "L4":

NET

"ECL OUT<11>"

NET

"ECL OUT<12>"

LOC = "L5";

NET

"ECL OUT<13>"

LOC = "K1";

NET

"ECL OUT<14>"

LOC = "K2"

"ECL OUT<15>"

LOC = "K3"

NET

LOC = "K4"

NET

"ECL OUT<16>"

LOC = "K5";

NET

"ECL_OUT<17>"

NET

"ECL OUT<18>"

LOC = "J5";

```

The pin names match with the schematic names and the names found throughout this manual. The engineering kit contains a reference project with the pin numbers defined and the bus interfaces implemented. A lot of time will be saved on the first implementation starting with the reference design. The pin-list and following definitions are for those who want to "do it themselves".

Numbers in [] are member numbers – bit position or vector number.

Numbers not in [] are channel numbers in most cases.

"N" as a suffix indicates active low

The direction and voltage level are defined for each term.

FDAT\_OUT = external FIFO output from Xilinx port

FDAT\_IN = external FIFO input to Xilinx port

PLL = Phase Locked Loop

WEN = Write Enable

REN = Read Enable

PAF = Programmable Almost Full

PAE = Programmable Almost Empty

FF = Full Flag

MT = Empty Flag

OSC is unconnected on the standard board.

The Address, Data\_IOP, ADS, BLAST, Ready, RST, W\_R signals are the interface to the PLX device. Please refer to the 9054 data manual if you are not using the Engineering kit.

## D100 Standard Pin Assignment

The pin assignment for the PCI-Serial-ECL P1 connector.

| IN IOD      | 10.100.4 |                             |

|-------------|----------|-----------------------------|

| INOP        | INOM     | 1 51                        |

| IN1P        | IN1M     | 2 52<br>3 53                |

| IN2P        | IN2M     | 3 53                        |

| IN3P        | IN3M     | 4 54                        |

| IN4P        | IN4M     | 5 55                        |

| IN5P        | IN5M     | 6 56                        |

| IN6P        | IN6M     | 7 57                        |

| IN7P        | IN7M     | 6 56<br>7 57<br>8 58        |

| IN8P        | IN8M     | 9 59                        |

| IN9P        | IN9M     | 10 60                       |

| IN10P       | IN10M    | 11 61                       |

| IN11P       | IN11M    | 12 62                       |

| 1N12P       | IN12M    | 13 63                       |

|             |          |                             |

| IN13P       | IN13M    | 14 64                       |

| IN14P       | IN14M    | 15 65                       |

| IN15P       | IN15M    | 16 66                       |

| IN16P       | IN16M    | 17 67                       |

| IN17P       | IN17M    | 18 68                       |

| IN18P       | IN18M    | 19 69                       |

| GND         | GND      | 20 70                       |

| GND         | GND      | 21 71                       |

| fused +5    | fused +5 | 22 72                       |

| fused +5    | fused +5 | 23 73                       |

| OUTOP       | OUTOM    | 24 74                       |

| OUT1P       | OUT1M    | 25 75                       |

| OUT2P       | OUT2M    | 26 76                       |

| OUT3P       | OUT3M    | 27 77                       |

| OUT4P       | OUT4M    | 28 78                       |

| OUT5P       | OUT5M    | 29 79                       |

| OUT6P       | OUT6M    | 30 80                       |

| OUT7P       | OUT7M    | 31 81                       |

| OUT8P       | OUT8M    | 32 82                       |

| OUT9P       | OUT9M    | 33 83                       |

| OUT10P      | OUT10M   | 34 84                       |

|             |          |                             |

| OUT11P      | OUT11M   | 35 85                       |

| OUT12P      | OUT12M   | 36 86                       |

| OUT13P      | OUT13M   | 37 87                       |

| OUT14P      | OUT14M   | 38 88                       |

| OUT15P      | OUT15M   | 39 89                       |

| OUT16P      | OUT16M   | 40 90                       |

| OUT17P      | OUT17M   | 41 91                       |

| OUT18P      | OUT18M   | 42 92                       |

| GND         | GND      | 43 93                       |

| GND         | GND      | 44 94                       |

| TTL_O       | TTL_1    | 45 95                       |

| TTL_2       | TTL_3    | 46 96                       |

| TTL_4       | TTL_5    | 47 97                       |

| TTL_6       | TTL_7    | 48 98                       |

| TTL_8       | TTL_9    | 49 99                       |

| TTL_10      | TTL_11   | 50 100                      |

|             | _        |                             |

| EICI IDE 10 |          | DCLSEDIAL FOL DAGO DINIGLIT |

FIGURE 19

PCI-SERIAL-ECL D100 PINOUT

Note 1: fused +5 is connected to P5V via a 2.54 "self healing" fuse... If you re

Note 1: fused +5 is connected to P5V via a 2.5A "self healing" fuse. If you prefer not to have power on the connector please alert the factory when placing your

order - we can leave the fuse off.

Note 2: INO..18P/M and OUTO..18P/M refer to the ECL IO.

## **Applications Guide**

## Interfacing

Some general interfacing guidelines are presented below. Do not hesitate to contact the factory if you need more assistance.

#### **ESD**

Proper ESD handling procedures must be followed when handling the PCI-Serial-ECL. The card is shipped in an anti-static, shielded bag. The card should remain in the bag until ready for use. When installing the card the installer must be properly grounded and the hardware should be on an anti-static work-station.

#### Start-up

Make sure that the "system" can see your hardware before trying to access it. Many BIOS will display the PCI devices found at boot up on a "splash screen" with the VendorlD and Cardld and an interrupt level. Look quickly! If the information is not available from the BIOS then a third party PCI device cataloging tool will be helpful. We use PCIView.

Watch the system grounds. All electrically connected equipment should have a fail-safe common ground that is large enough to handle all current loads without affecting noise immunity. Power supplies and power consuming loads should all have their own ground wires back to a common point.

## Construction and Reliability

PCI Modules while commercial in nature can be conceived and engineered for rugged industrial environments. The PCI-SERIAL-ECL is constructed out of 0.062 inch thick FR4 material.

Through hole and surface mounting of components are used. High insertion and removal forces are required, which assists in the retention of components. If the application requires unusually high reliability or is in an environment subject to high vibration, the user may solder the corner pins of each socketed IC into the socket, using a grounded soldering iron.

The D100 connector has Phosphor Bronze pins with Nickel plating for durability and Gold plating on the contact area on both plugs and receptacles. The connectors are keyed and shrouded. The pins are rated at 1 Amp per pin, 500 insertion cycles minimum [at a rate of 800 per hour maximum]. These connectors make consistent, correct insertion easy and reliable.

#### Thermal Considerations

The PCI-SERIAL-ECL design consists of CMOS circuits. The power dissipation due to internal circuitry is very low. The installed IP Modules may require forced-air cooling. With the one degree differential temperature to the solder side of the board external cooling is easily accomplished.

## Warranty and Repair

Dynamic Engineering warrants this product to be free from defects in workmanship and materials under normal use and service and in its original, unmodified condition, for a period of one year from the time of purchase. If the product is found to be defective within the terms of this warranty, Dynamic Engineering's sole responsibility shall be to repair, or at Dynamic Engineering's sole option to replace, the defective product. The product must be returned by the original customer, insured, and shipped prepaid to Dynamic Engineering. All replaced products become the sole property of Dynamic Engineering.

Dynamic Engineering's warranty of and liability for defective products is limited to that set forth herein. Dynamic Engineering disclaims and excludes all other product warranties and product liability, expressed or implied, including but not limited to any implied warranties of merchandisability or fitness for a particular purpose or use, liability for negligence in manufacture or shipment of product, liability for injury to persons or property, or for any incidental or consequential damages.

Dynamic Engineering's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Dynamic Engineering.

## Service Policy

Before returning a product for repair, verify as well as possible that the suspected unit is at fault. Then call the Customer Service Department for a RETURN MATERIAL AUTHORIZATION (RMA) number. Carefully package the unit, in the original shipping carton if this is available, and ship prepaid and insured with the RMA number clearly written on the outside of the package. Include a return address and the telephone number of a technical contact. For out-of-warranty repairs, a purchase order for repair charges must accompany the return. Dynamic Engineering will not be responsible for damages due to improper packaging of returned items. For service on Dynamic Engineering Products not purchased directly from Dynamic Engineering contact your reseller. Products returned to Dynamic Engineering for repair by other than the original customer will be treated as out-of-warranty.

#### Out of Warranty Repairs

Out of warranty repairs will be billed on a material and labor basis. The current minimum repair charge is \$100. Customer approval will be obtained before repairing any item if the repair charges will exceed one half of the quantity one list price for that unit. Return transportation and insurance will be billed as part of the repair and is in addition to the minimum charge.

#### For Service Contact:

Customer Service Department Dynamic Engineering 435 Park Dr. Ben Lomond, CA 95005 831-336-8891 831-336-3840 fax support@dyneng.com

## Specifications

PCI Interfaces: PCI Interface 33 MHz. 32 bit

Access types: Configuration and Memory space utilized

CLK rates supported: 33 MHz. PCI, PLL with 66 MHz reference to provide programmable

frequencies.

Memory FIFO memory is provided to support DMA 1K x 32. In addition 128K x32

FIFO provided to support Xilinx data flow with TX and RX.

10 19 ECL Transmitters. 19 ECL receivers. 12 TTL with programmable

direction.

Interface: D100 connector. [AMP] 787082-9 is the board side part number

Software Interface: Control Registers within Xilinx.

Initialization: Programming procedure documented in this manual

Access Modes: Registers on longword boundary. Standard target access read and write to

registers and memory. DMA access to memory.

Access Time: no wait states in DMA modes. 1-2 wait states in target access to Xilinx.

Interrupt: 1 interrupt to the PCI bus is supported with multiple sources. The interrupts are maskable and are supported with a status register.

miori apos di o masicasio dila di o sapportoa vitir a statas i og

Onboard Options: All Options are Software Programmable

Dimensions: half length PCI board.

Construction: FR4 Multi-Layer Printed Circuit, Through Hole and Surface Mount

Components. Programmable parts are socketed.

Power: 5V from PCl bus. Local 3.3 and 2.5, 1.8 and -5 created with on-

board power supplies.

User 8 position software readable switch

1 software controllable LED's

1 Power LED

#### Order Information

Standard temperature range 0-70°C

PCI-SFRIAL-FCI http://www.dyneng.com/pci serial ecl.html

half length PCI card with user re-configurable Xilinx, 38 ECL,

12 TTL 10, 1 PLL

Extended temperature range -20 - 85°C

PCI-SERIAL-ECL-ET http://www.dyneng.com/pci serial ecl.html

half length PCI card with user re-configurable Xilinx, 38 ECL,

12 TTL 10, 1 PLL

PCI-SERIAL-ECL-ENG Engineering Kit for the PCI-SERIAL-ECL

> Software, Schematic, Cable and HDEterm100, reference Xilinx implementation. See webpage for more details and

options including software drivers.

HDEterm100 http://www.dyneng.com/HDEterm100.html

> 100-pin connectors (2) matching the PCI-Serial-ECL D100 interconnected with 100 screw terminals. DIN rail mounting. Optional terminations and testpoints.

HDEcable 100 http://www.dyneng.com/HDEcabl100.html

100 pin connector matching PCI-Serial-ECL and

HDEterm100. Length options

All information provided is Copyright Dynamic Engineering